為了提高肖特基二極管的雪崩耐量,以避免元器件的雪崩損壞(huài),三安集成電路在18年10月29日申請了一項名為“新型碳化矽結勢壘肖特(tè)基二極管及其製作方法”的發明專(zhuān)利(申請號:201811267285.X),申請人為廈門市三安集成電路有限公司。

根據(jù)目前該專利公開的資料,讓我們(men)一起來(lái)看看這項肖特(tè)基(jī)二(èr)極管專利吧。

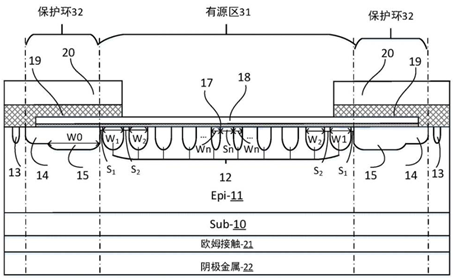

如上(shàng)圖為新型碳化矽結勢壘肖特基二極管的分層結(jié)構圖,該結構中包括層疊設置的(de)第一導電類型碳化矽襯底10和第一導電類(lèi)型碳(tàn)化矽外(wài)延層11。第一導電類型碳化矽外延層(céng)的上表麵由中心向外依次(cì)設置有有(yǒu)源區31、保護環32和第二(èr)導電類型終(zhōng)端場限環13,有源區包括(kuò)間(jiān)隔設置的多個第二導電類型結(jié)勢壘區12。

沿著保護環向有源區的中心的方向,相鄰第二導(dǎo)電類型結勢壘區(qū)的間距逐漸增大,且第(dì)二導電類型結勢壘區的寬度逐漸(jiàn)減小。有源區包(bāo)括n個第二導電類型結勢壘區,靠近保護環的第一個結勢壘區的寬度W1為1-15um;保護(hù)環(huán)32與第一個結勢壘區的間距S1為0.5-8um;第n個第二導電類型結勢壘區的寬度Wn為0 .5-4um,第n-1個第二導電類型結勢(shì)壘區與第n個第二導電類型結勢壘區的間距(jù)Sn為5-10um。

這樣的結構,主要(yào)是因為結勢壘區(qū)之間的間隔逐漸增(zēng)大後,當施加的反向偏壓不斷增(zēng)加,有源區靠近中心處結勢壘區之間的間距較大,肖特基結的電場強度較大,由於肖特基效應,導致該區域的肖特基勢壘高度降低,成為擊穿薄弱(ruò)點,因此將擊穿點引入到有(yǒu)源區(qū)中心區域(yù),增加了雪崩狀態下的散熱麵積,從(cóng)而提高了雪崩耐(nài)量!

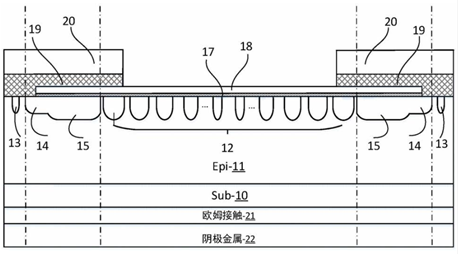

如上圖所示,每一(yī)個第二導電類型結勢壘12區包括一個子結勢壘區,並且第(dì)二導電類型結勢壘(lěi)區為長條形(xíng),沿著保護環的兩側(cè)向(xiàng)有源區31的中心的方向,相鄰第(dì)二導電類型結勢壘區的間距逐漸增大,且第二導電類型結勢壘區的寬度逐漸減小(xiǎo)。

下(xià)麵我們再來(lái)聊聊這種新型碳化矽(guī)結勢壘肖特基二極管的製作方法,如下圖所示。

首先,準備碳化矽襯底10,其電阻率為0.001-0.05Ω·cm,厚(hòu)度200-380um。在碳化矽襯底上(shàng),生(shēng)長第一導電類型的碳化矽外延層11,在碳化矽外延層上表麵,通過澱積SiO2、光刻、選擇性離子注入(rù)形(xíng)成(chéng)間隔設置的多個第二(èr)導電類(lèi)型結勢壘區(qū)12和深結15,深結位(wèi)於(yú)第二導(dǎo)電類型結(jié)勢壘區外,並且深結(jié)和第二導電類型結(jié)勢壘區的深度相同。

多個第二導電類型結勢壘區沿(yán)著由(yóu)外向內的方向,相鄰第二導電(diàn)類型結勢壘區(qū)的間距逐漸增大,且第二導電類(lèi)型結勢(shì)壘區12的寬度逐漸減小。在(zài)碳化矽外延層上表麵,通過光刻、選擇性離子(zǐ)注入形(xíng)成深度相同的第二導電類型終端場限(xiàn)環13和淺結(jié)14。

接著,通過物理研磨,將碳化矽襯底的背麵減(jiǎn)薄至200-220um,在碳化矽襯底的背麵通過電子束蒸發澱積金屬Ni,並在900℃下退火形成歐姆接觸21,在(zài)碳化矽外延層上表麵,通過電子束蒸發或(huò)濺鍍(dù),澱積金屬Ti,並在500℃下退火形成(chéng)肖特基金屬17。

最後,在肖特基金屬(shǔ)的上表麵(miàn),通過電子(zǐ)束蒸發澱(diàn)積金屬Al,形成陽極18,在碳化矽外延層上表麵及陽極金(jīn)屬的上表麵,通過PECVD,澱積形成SiO2/Si3N4層,通過光刻、形成鈍(dùn)化層19,在鈍化層的上表(biǎo)麵,通過(guò)澱積、光刻形成保護層20,在歐姆接觸21的(de)下表麵,通過澱積,形成TiNiAg陰極金(jīn)屬22。

以上就是三安集成電路的新型碳化矽結勢壘肖特(tè)基二極管發明(míng)專利(lì),二極管是電子產品的主要部件之一,優質的二極管是保證電子產品穩定性的源(yuán)頭,而三安(ān)集成電路這項專利正好填補了這方麵的空缺,從而使得電子產品的質量大大提高!